# **Energy Efficient Interfaces**

# OIF Interoperability Demo ECOC 2024

Copyright © 2024 OIF

# Energy Efficient Interfaces @ ECOC 2024

### Energy Efficient Interfaces (EEI)

### EEI Interoperability agreements

- Co-Packaging Framework Document

- 3.2T Optical Module for Co-Packaging Project

- ELSFP Project

- Electrical Interfaces for Co-Packaging

### Interoperability Demonstrations

# The Challenge!

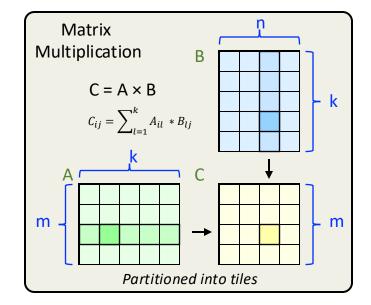

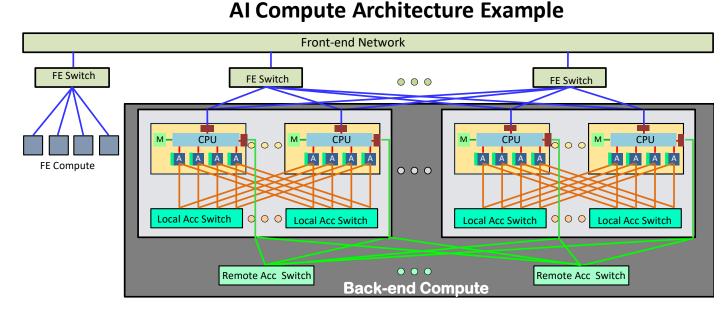

- Al training utilizes large quantities of matrix multiplication

- GPUs are designed to accelerate "multiply and add" operations used in AI matrix multiplication

- Each row in matrix A is paired with every column in matrix B Lots of computation with lots of parameters!

- Large AI models can partition the computation into smaller chunks

- Tile computations can be handed off to clusters of local and remote compute accelerators

- However, the completion of a tile in matrix C must wait for all contributing tiles to complete

- The time to complete the computation depends on:

- Computation speed

- Interconnect bandwidth

- Memory speed

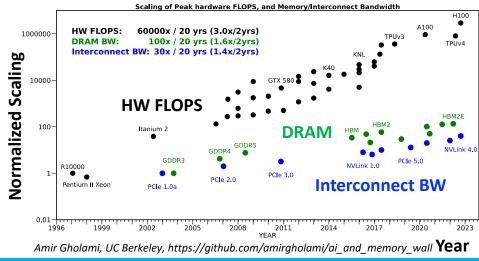

Al scale-up will drive adoption of optical chiplets to achieve lower latency, energy efficient, & cost-effective interconnections to support large AI models

# What approaches can we use?

- What is needed?

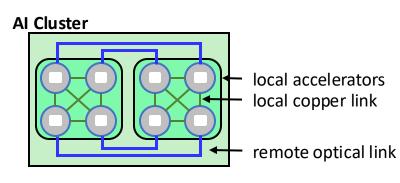

- Larger local clusters interconnected with short links

- Energy efficient, high-speed, low latency, dense interconnects that can scale

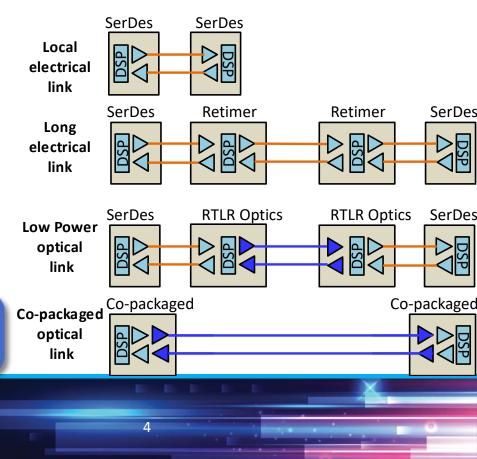

- Copper Links

- Copper is ideal for local connections

- As the data rates increase, pure electrical link reach becomes shorter

- Reach can be extended with additional DSP capability and/or with the addition of retimers, trading off additional latency and power

- Optical Links

- With some addition of E-O power, the electrical signaling can be converted to optical and then travel without needing additional retimers to restore the signal

- If the electro-optical conversion is co-packaged with the ASIC, additional power and latency can be saved

AI scale-up will drive adoption of optical chiplets to achieve lower latency, energy efficient, & cost-effective interconnections to support large AI models

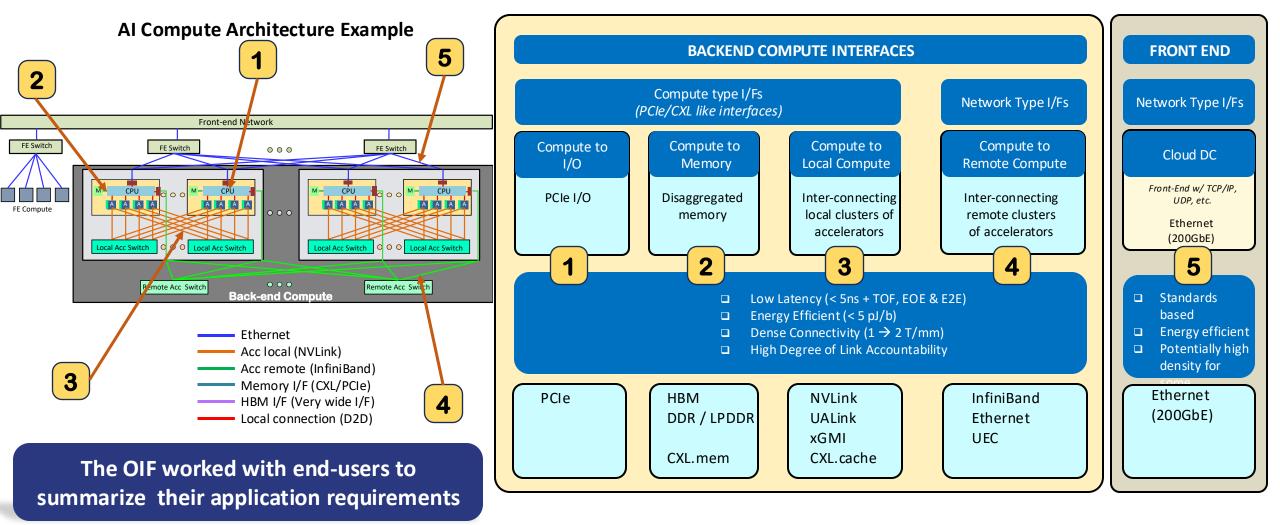

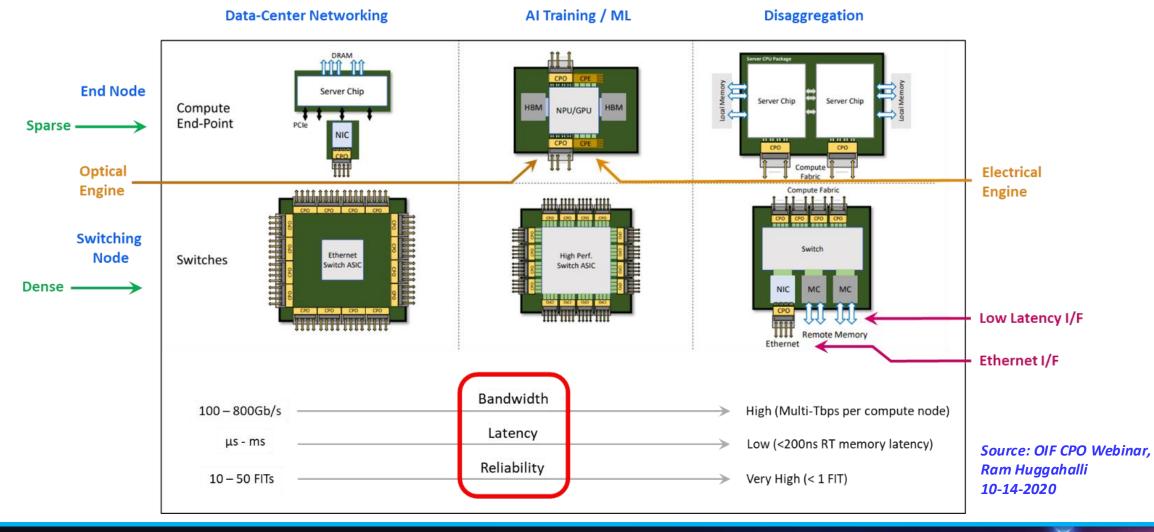

# Applications for energy efficient links for Al

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF Adapted from oif2023.269, Ram Huggahalli, Microsoft

# What kinds of Energy Efficient links are needed?

- Energy efficient, high-speed, low latency interconnects

- PCIE-like

- Memory

- Local Accelerator interconnect

- I/O

- Low latency Ethernet

- Remote accelerator interconnect

- Ethernet —

Back-end compute can leverage co-packaged solutions using optical chiplets for dense, energy efficient, low latency interconnections

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF

# What is the OIF doing?

### **OIF's Co-Packaging Projects**

✓ Co-packaging Framework Project

OIF-Co-Packaging-FD-01.0 – Co-Packaging Framework Document

### $\checkmark$ 3.2T Co-packaged Optical Engine

<u>OIF-Co-Packaging-3.2T-Module-01.0 – Implementation Agreement for a 3.2Tb/s Co-Packaged (CPO) Module</u>

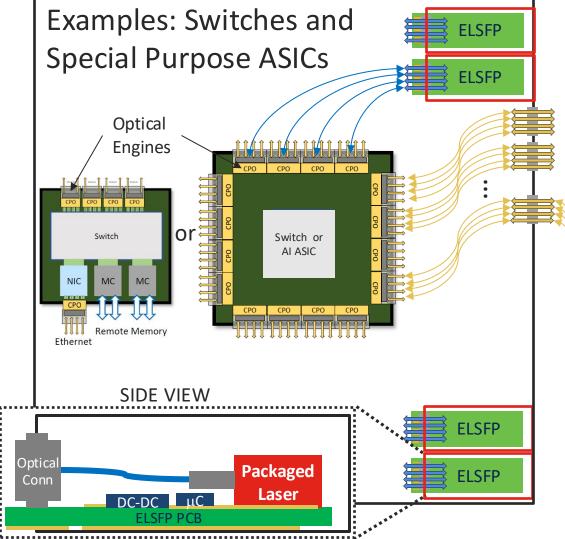

### ✓ External Laser Source (ELSFP)

External Laser Small Form Factor Pluggable (ELSFP) Implementation Agreement (August 2023)

#### ✓ Management Interface for ELSFP

<u>OIF-ELSFP-CMIS-01.0 – Implementation Agreement for External Laser Small Form</u> Factor Pluggable (ELSFP) CMIS

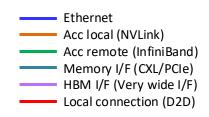

### **Energy Efficient Interfaces for AI**

#### System Vendor Requirements Document for Energy Efficient Interfaces

Document the EEI requirements as provided by the end-users for AI/ML optical and electrical links

### **Energy Efficient Interface Framework**

Study and initiate new standards for dense, low power, low latency links for AI/ML

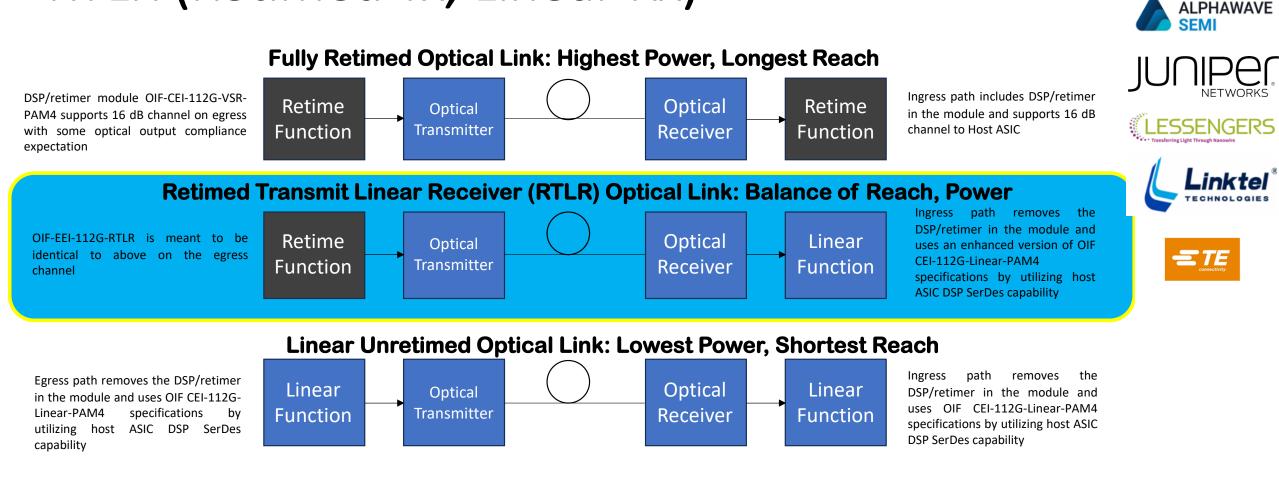

#### **RTLR Project (Retimed Transmitter, Linear Receiver)**

Address lower latency and low power applications utilizing transmit retimed optical transceivers (e.g. Ethernet, UEC, etc.)

### **COI Project (Compute Optics Interface)**

Address energy efficient, low latency photonic interfaces for transport of traffic for AI scale-up applications (e.g. PCIe, NVLink, UALink, etc.)

## **OIF Projects Addressing Next Gen AI Compute Interfaces**

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF Adapted from oif2023.269, Ram Huggahalli, Microsoft

# Energy Efficient Interfaces @ ECOC 2024

Energy Efficient Interfaces (EEI)

### EEI Interoperability agreements

- Co-Packaging Framework Document

- **3.2T** Optical Module for Co-Packaging Project

- ELSFP Project

- Electrical Interfaces for Co-Packaging

### Interoperability Demonstrations

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF

q

### Co-Packaging Application Spaces Framework Project

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF

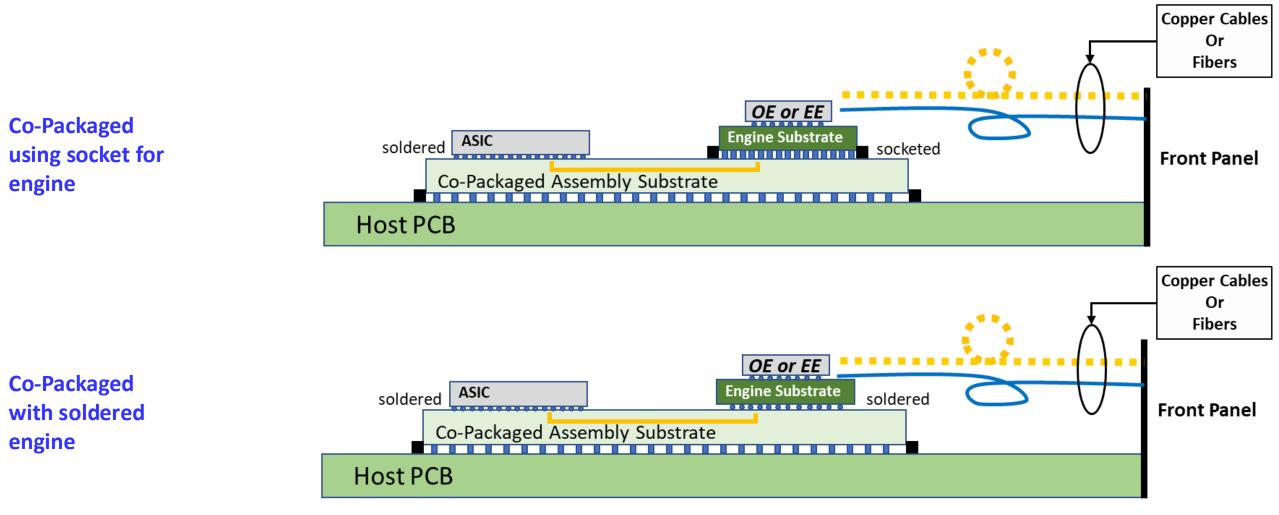

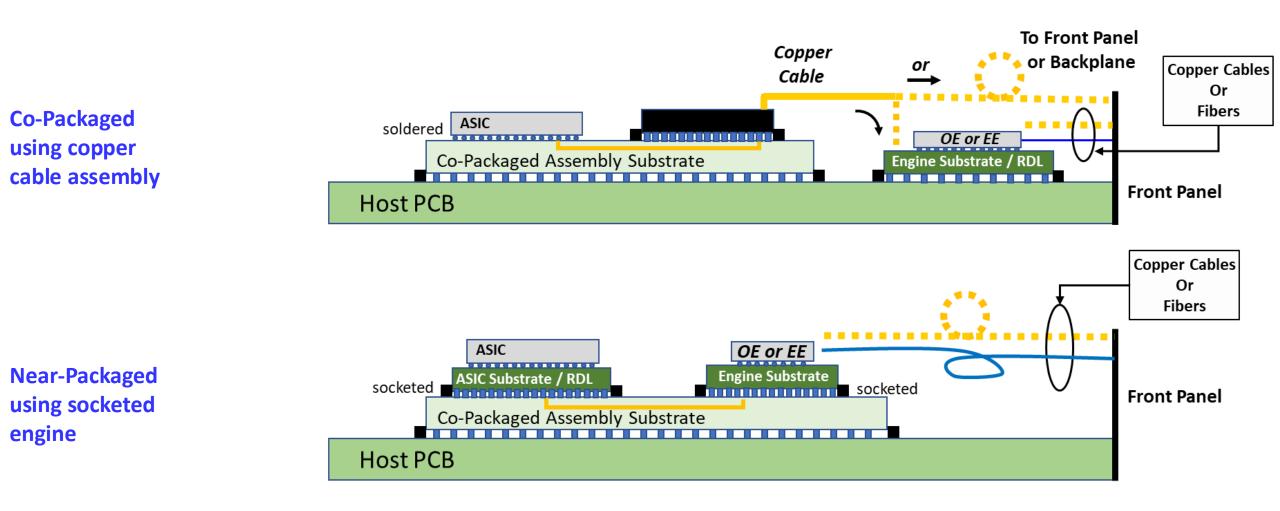

### Co-Packaging Architectures (1) Framework Project

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF

### Co-Packaging Architectures (2) Framework Project

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 <u>OIF</u>

# Interfaces Studied for Interoperability

Framework Project

### Application Example

- Switch Generation: 51.2Tb/s

- Lane Speed: 106 Gb/s

- Interface Architecture: XSR based AUI, 400G-FR4 PMD

- Motivation: System power reduction, ecosystem & operational readiness

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF **Reliability and Repairability**

# Energy Efficient Interfaces @ ECOC 2024

Energy Efficient Interfaces (EEI)

- EEI Interoperability agreements

- Co-Packaging Framework Document

- 3.2T Optical Module for Co-Packaging Project

- **ELSFP** Project

- Electrical Interfaces for Co-Packaging

### Interoperability Demonstrations

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF

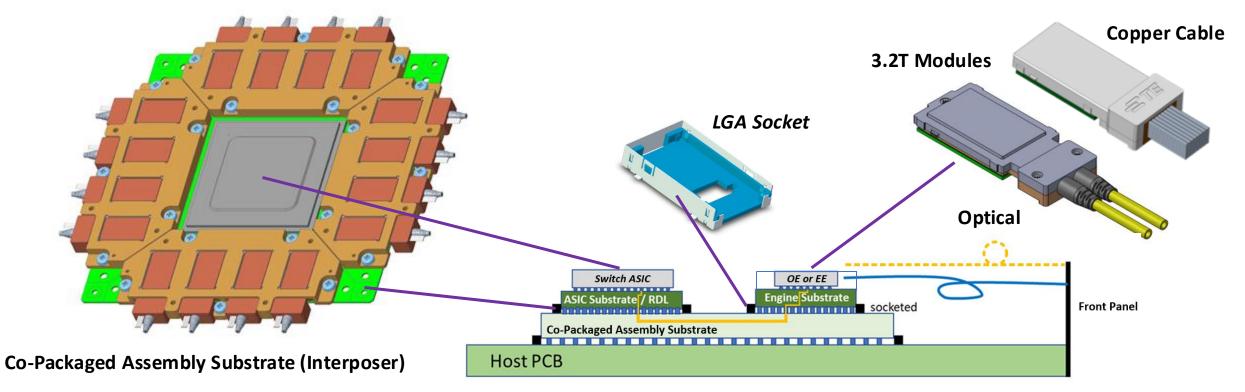

## Example System Attachment 3.2T Optical Module

• 16 x 3.2T Modules = 51.2T Switch Capacity

**Channel components cross-section**

15

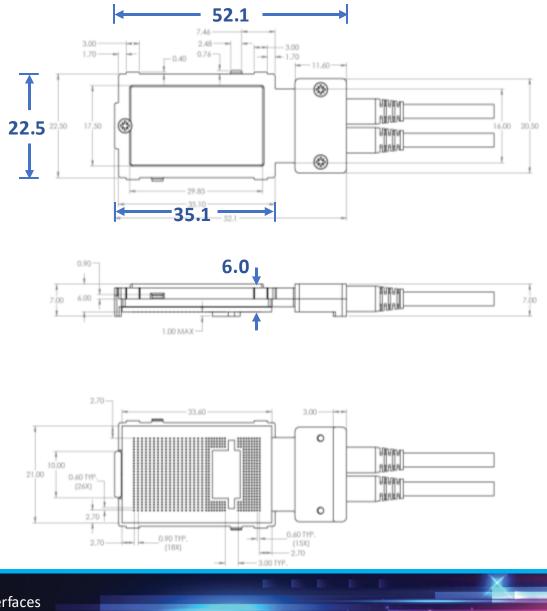

## **3.2T Module Dimensions** 3.2T Optical Module

- 32 x 112G XSR to Standard Optics:

- 8 x 400G DR4

- 8 x 400G FR4 (incl. 200G mode)

- Copper Cable Assembly compatible

- Power capability:

- 56W (Internal Laser option)

- 48W (External Laser option)

16

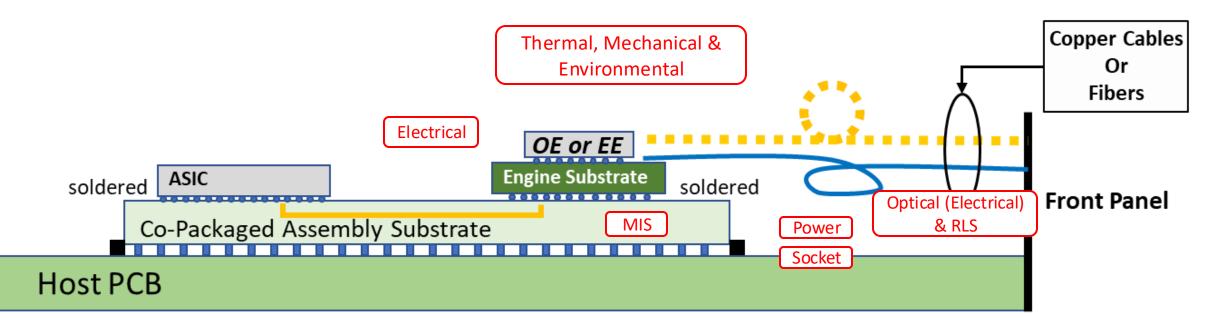

## LGA Pin Map 3.2T Optical Module

- Supply rails: 12V, 3.3V, 2.6V, 1.8V, 1.2V, 0.9V, 0.7V

- Comms Electrical: 1.2V SPI

- Comms protocol: CMIS

- 400G and 800G (2x400G) port grouping defined

- For low power modes and 2x400G-FR4 cable assignment

|                     |            |             |            |            |            |             |            |             |              |                              |            |                |                     |                     |            |                |            |         |            |                     |                 |     |                                         |                 |              |    | 00<br>X |    |    |               | t<br>Gro          | วน          | pi                    | ng            |                | VCC<br>VCC                           | C_1P<br>C_1P<br>C_2P |

|---------------------|------------|-------------|------------|------------|------------|-------------|------------|-------------|--------------|------------------------------|------------|----------------|---------------------|---------------------|------------|----------------|------------|---------|------------|---------------------|-----------------|-----|-----------------------------------------|-----------------|--------------|----|---------|----|----|---------------|-------------------|-------------|-----------------------|---------------|----------------|--------------------------------------|----------------------|

|                     |            |             | Ingr       | ess,       | to S       | Swit        | ch         |             |              |                              |            |                |                     | Egre                | ss, t      | to Fi          | ber        |         |            |                     |                 |     |                                         |                 |              |    |         |    |    |               |                   |             | •                     | -             |                |                                      | C_3P<br>C_12         |

|                     | A          | в           | С          | D          | Е          | F           | G          | н           | J            | ĸ                            | L          | м              | N                   | Р                   | R          | т              | U          | ۷       | ¥          | Y                   | AA              |     | AC AI                                   |                 | E AF         | AG | AH      | AJ | AK | _             | AM A              | -           |                       |               |                | AV A                                 |                      |

| 27                  | GND        | GND         | GND        | GND        | GND        | GND         | GND        | GND         | GND          | VCC_0P7                      | GND        | GND            | GND                 | GND                 | GND        | GND            | GND        | GND     | GND        | VCC_<br>0P9         | VCC_<br>0P9     |     | /CC_ VCI<br>0P9 0P                      |                 |              |    |         |    |    | GND           | 3P3 3F            | GN          | PZ                    | GND           |                | /CC_1 C                              |                      |

| 26                  | GND        | HBX_E1F     | GND<br>GND | HBX_F1     | GND        | HRX_GIP     | GND<br>GND | HRX_HIP     | GND          | VCC_0P7<br>A<br>VCC_0P7<br>A | GND        | HTX_EIP        | GND                 | HTX_FIP             | GND<br>GND | HTX_GIP        | GND<br>GND | HTX_HIF | GND        | GND<br>REFC         | GND<br>REFC     |     | /CC_ GN<br>0P9 GN<br>/CC_ GN            | _               | VCC          |    |         |    |    | 3P3<br>VCC    | 3P3 GM            | 2000        | 1 VCC                 | 1 VCC 1       | GND            | /CC_1 VD<br>P8 P<br>/CC 1 VD         | C_1<br>8<br>C_1      |

| 25<br>24            | GND        | GND         | GND        | GND        | GND        | GND         | GND        | GND         | GND          | A<br>VCC_0P7                 | GND<br>GND | HTX_EIN<br>GND | GND                 | HTX_F1N<br>GND      | GND        | HTX_GIN<br>GND | GND        | HTX_HIN | GND<br>GND | LK_1P<br>GND        | LK_1N           |     | /CC_ GN<br>0P9 GN<br>/CC_ VCI<br>0P9 0P |                 | C VCC        |    | -       |    |    | 3P3<br>VCC_   | GND GN            | 3000        |                       | P2<br>1 VCC_1 | GND            | /CC_1 VD<br>P8 P<br>/CC_1 VD<br>P8 P | 28<br>C_1            |

| 23                  | GND        | HBX E2      | GND        | HBX E2     | GND        | HBX_G       | GND        | HBX_H2      | GND          | A<br>VCC_0P7                 | GND        | HTX_E2P        | GND                 | HTX_F2P             | GND        |                | GND        | HTX_H2F | GND        | VCC_<br>0P9         |                 | SHU | 0P9 0P                                  | 9 0P            | 9 0P9        |    | -       |    |    | 3P3           | GND GN            |             | P2                    |               |                | P8 P                                 |                      |

| 22                  | GND        | HBX_E2      | GND        | HBX_F2     | GND        | P<br>HRX_G2 | GND        | P<br>HRX_H2 | GND          | A<br>VCC_0P7                 | GND        | HTX_E2N        | GND                 | HTX_F2N             | GND        | HTX_G2N        | GND        | HTX_H2  | GND        | 0P9<br>VCC_<br>0P9  |                 |     |                                         | -               | -            | +  | +       |    |    | -             | VC                | C_ VCC      |                       |               | VCC_           | VCC_ VC                              | 10_                  |

| 21                  | GND        | GND         | GND        | GND        | GND        | GND         | GND        | GND         | GND          | A<br>VCC_0P7                 | GND        | GND            | GND                 | GND                 | GND        | GND            | GND        | GND     | GND        | 0P9<br>VCC_<br>0P9  |                 |     |                                         | -               |              | 1  |         |    |    |               | 0P<br>VC<br>0P    |             | B 0P78                | GND           | GND            | 2P6 2F<br>VCC_ VC<br>2P6 25          | P6<br>1C_            |

| 20                  | GND        | HBX_E3      | GND        | HBX_F3     | GND        | HRX_G       | GND        | HBX_H3      | GND          | VCC_0P7                      | GND        | HTX_E3P        | GND                 | HTX_F3P             | GND        | HTX_G3P        | GND        | нтх_нзя | GND        | VCC_<br>0P9         |                 |     |                                         |                 |              | 1  |         |    |    |               | VC                | C_ 01       | 200                   | GND           | GND            | GND GN                               | ND                   |

| 19                  | GND        | HBX_E3      | GND        | HBX_F3     | GND        | HRX_GC      | GND        | HRX_H3<br>N | GND          | VCC_0P7                      | GND        | HTX_E3N        | GND                 | HTX_F3N             | GND        | HTX_G3N        | GND        | нтх_нам | GND        | VCC_<br>0P9         |                 |     |                                         |                 |              | 1  |         |    |    |               | VC<br>0P          | 0_<br>78 GN | D VCC                 | GND           | CLK_1          | CLK_1 G                              | ND                   |

| 18                  | GND        | GND         | GND        | GND        | GND        | GND         | GND        | GND         | GND          | VCC_0P7                      | GND        | GND            | GND                 | GND                 | GND        | GND            | GND        | GND     | GND        | VCC_<br>0P9         |                 |     |                                         |                 |              | 1  |         |    |    |               | VC<br>0P          | C VCC       | B 0P78                | GND           | GND            | GND GI                               | ND                   |

| 17                  | GND        | HBX_E48     | GND        | HBX_F4     | GND        | HRX_G4<br>P | GND        | HBX_H4<br>P | GND          | VCC_0P7<br>A                 | GND        | HTX_E4P        | GND                 | HTX_F4P             | GND        | HTX_G4P        | GND        | HTX_H4F | GND        | VCC_<br>0P9         |                 |     |                                         |                 |              |    |         |    |    |               | VC<br>0P          | 7B GIN      | 0676                  | GND           | INT I          | RSTN GP                              | ND                   |

| 16                  | GND        | HBX_E4      | GND        | HBX_F4     | GND        | HRX_G4      | GND        | HBX_H4      | GND          | VCC_0P7<br>A                 | GND        | HTX_E4N        | GND                 | HTX_F4N             | GND        | HTX_G4N        | GND        | HTX_H40 | GND        | VCC_<br>0P9         |                 |     |                                         |                 |              |    |         |    |    |               | VC<br>0P          | 7B          | - 0P76                | GND           |                | GND GM                               | ND                   |

| 15                  | GND        | GND         | GND        | GND        | GND        | GND         | GND        | GND         | GND          | VCC_0P7                      | GND        | GND            | GND                 | GND                 | GND        | GND            | GND        | GND     | GND        | VCC_<br>0P9         |                 |     |                                         |                 |              |    |         |    |    |               | VC<br>0P          | 7B 0P1      | B 0P78                | GND           | SPLC S         | OSI GI                               |                      |

| 14                  | ACC_0P7    | VCC_0P      | VCC_0P     | A A        | A          | A A A       | A          | A           | VCC_0P7<br>A | VCC_0P7                      | GND        | VCC_0P9        | -                   | 9 VCC_0P9           | VCC_0P9    | VCC_0P9        | VCC_0P9    | -       | VCC_0P9    | VCC_<br>0P9         |                 |     |                                         |                 |              | 1  | _       |    |    |               | VC<br>0P<br>VC    | 7B UN       |                       |               | SPI_M 1<br>ISO |                                      |                      |

| 13                  | GND        | GND         | GND        | GND        | GND        | GND         | GND        | GND         | GND          | VCC_0P7<br>A                 | GND        | GND            | GND                 | GND                 | GND        | GND            | GND        | GND     | GND        | VCC_<br>0P9         |                 |     | _                                       | _               |              | 1  | -       |    |    |               | 0P<br>VC          | -           | B 0P78                |               |                | GND GN                               |                      |

| 12                  | GND        | HBX_A1F     | GND        | HRX_B1     | GND        | HRK_CIP     | GND        | HRK_DIF     | GND          | VCC_0P7<br>A<br>VCC_0P7      | GND        | HTX_AIP        | GND                 | HTX_BIP             | GND        | HTX_CIP        | GND        | HTX_DIF | GND        | VCC_<br>0P9<br>VCC  |                 | _   | _                                       | +               | _            | +  | -       |    |    | _             | 0P<br>VC          | 7B Gird     | 0P7                   |               | 2              | /CC_1 GP                             |                      |

| 11<br>18            | GND<br>GND | GND         | GND<br>GND | HRX_B1     | GND<br>GND | GND         | GND<br>GND | GND         | GND<br>GND   | VCC_0P7<br>A<br>VCC_0P7<br>A | GND<br>GND | HTX_AIN<br>GND | GND<br>GND          | HTX_BIN             | GND<br>GND |                | GND<br>GND |         | GND<br>GND | VCC_<br>0P9<br>VCC_ | $ \rightarrow $ |     | _                                       | -               |              | +  |         |    |    | -             | 0P<br>VC          | 7B GIN      | C_ VCC                | GND           |                | VID_1 GP                             |                      |

| 1U<br>9             | GND        | HEK_A2      |            | HRX_B      | GND        | HRX_C       | GND        | HRX_D2      | GND          | Ā<br>VCC_0P7<br>Ā            | GND        | HTX A2P        | GND                 | HTX_B2P             | GND        | HTX C2P        | GND        | HTX_D2F | GND        | VCC_<br>0P9<br>VCC_ | $\vdash$        |     |                                         | -               |              | +  | -       |    |    | -             | 0P<br>VC          | 7B OPT      | B 0P78                | -             | CLK_2          | MON                                  |                      |

| 8                   | GND        | P<br>HRK_A2 | GND        | P<br>HRX_B | GND        | P<br>HRX_C3 | GND        | P<br>HRX_D2 | GND          | A<br>VCC_0P7                 | GND        | HTX_A2N        | GND                 | HTX_B2N             | GND        | HTX_C2N        | GND        | HTX_D2  | GND        | 0P9<br>VCC_<br>0P9  | $\vdash$        |     |                                         | +               | -            | +  | +       |    |    | -             | 0P<br>VC          | лы<br>0_ ам | VCC                   | GND           | -              | GND GM                               |                      |

| 7                   | GND        | GND         | GND        | GND        | GND        | GND         | GND        | GND         | GND          | A<br>VCC_0P7                 | GND        | GND            | GND                 | GND                 | GND        | GND            | GND        | GND     | GND        | 0P9<br>VCC_<br>0P9  | +               |     |                                         | +               |              | +  |         |    |    | -             | 0P<br>VC          | в           | 0P76<br>VCC<br>8 0P76 | GND           | GND            | VCC_ VC                              | C_                   |

| 6                   | GND        | HEK_AS      | GND        | HEX_B      | GND        | HRX_C:      | GND        | HRX_D3      | GND          | VCC_0P7                      | GND        | HTX_A3P        | GND                 |                     | GND        | HTX_C3P        | GND        | HTX_D3P | GND        | VCC_<br>0P9         | +               |     |                                         | +               | 1            | +  | +       |    |    | -             | VC<br>0P          |             | 0 VCC<br>8 0P78       |               | VCC_           | 2P6 20<br>2P6 20                     | P6<br>30_<br>P6      |

| 5                   | GND        | HFIX_AS     | GND        | HRX_B      | GND        | HRX_C3      | GND        | HRX_D3<br>N | GND          | VCC_0P7                      | GND        | HTX_A3N        | GND                 | HTX_B3N             | GND        | HTX_CON        | GND        |         | GND        | VCC_<br>0P9         |                 |     |                                         | +               |              | 1  | 1       |    |    | -             | GN                |             |                       |               |                | GND GN                               | ND                   |

| ٠                   | GND        | GND         | GND        | GND        | GND        | GND         | GND        | GND         | GND          | VCC_0P7                      | GND        | GND            | GND                 | GND                 | GND        | GND            | GND        | GND     | GND        | GND                 |                 |     | /CC_ VCI<br>0P9 0P                      | 0_ VCC<br>9_0P1 | 0_ VCC       | -  |         |    |    | VCC_<br>3P3   | GND GN            |             | 1 VCC_                | 1 VCC_1<br>P2 | GND            | P8 P                                 |                      |

| 3                   | GND        | HRX_A4      | GND        | HRX_B      | GND        | HRX_C4      | GND        | HRX_D4      | GND          | VCC_0P7<br>Å                 | GND        | HTX_A4P        | GND                 | HTX_B4P             | GND        | HTX_C4P        | GND        | HTX_D4P | GND        | REFC<br>LK_2P       | REFC<br>LK_2N   | GND | OP9 GN                                  |                 |              |    |         |    |    | VCC_<br>3P3   | /CCGN             | ID VCC      | 1 VCC                 | 1 VCC_1<br>P2 | GND            | /CC_1 VO<br>P8 P                     | C_1<br>98            |

| 2                   | GND        | HRK_A4      | GND        | HRX_B      | GND        | HRX_CA      | GND        | HRX_D4      | GND          | VCC_0P7<br>Ā                 | GND        | HTX_A4N        | GND                 | HTX_B4N             | GND        | HTX_C4N        | GND        |         | GND        | GND                 | GND             |     | OP9 GN                                  |                 | D VCC<br>0P9 | 7  |         |    |    | VCC_ 1<br>3P3 | 3P3 GM            |             | P VCC_<br>P2          | 1 GND         | GND            | /CC_1 VD<br>P8 P                     | C_1<br>98            |

| 1                   | GND        | GND         | GND        | GND        | GND        | GND         | GND        | GND         | GND          | VCC_0P7                      | GND        | GND            | GND                 | GND                 | GND        | GND            | GND        | GND     | GND        | VCC_<br>0P9         |                 |     | /CC_ VCI<br>0P9 0P                      |                 |              |    |         |    |    | GND           | 700_ VC<br>3P3 3F | GN GN       | 12                    |               |                | /CC_1 C                              | _                    |

|                     | ^          | в           | С          | D          | Е          | F           | G          | н           | J            | ĸ                            | L          | м              | N                   | Р                   | в          | т              | U          | v       | v          | Y                   | AA              | AB  | AC AI                                   | D AE            | AF           | AG | AH      | AJ | AK | AL            | AM A              | N AF        | P AR                  | AT            | AU             | AV A                                 | •                    |

|                     |            |             |            |            |            |             |            |             |              |                              |            |                |                     |                     |            |                |            |         |            |                     |                 |     |                                         |                 |              |    |         |    |    |               |                   |             |                       |               | Το             | p١                                   | /ie                  |

| RF region           |            |             |            |            |            |             |            |             |              |                              |            |                | DC/Low-Speed region |                     |            |                |            |         |            |                     |                 |     |                                         |                 |              |    |         |    |    |               |                   |             |                       |               |                |                                      |                      |

| 0.9mm x 0.6mm pitch |            |             |            |            |            |             |            |             |              |                              |            |                | C                   | 0.6mm x 0.6mm pitch |            |                |            |         |            |                     |                 |     |                                         |                 |              |    |         |    |    |               |                   |             |                       |               |                |                                      |                      |

VCC 0P7A VCC OP7B VCC 0P9

Energy Efficient Interfaces **OIF's ECOC Interoperability Demo** Copyright @ 2024 OIF

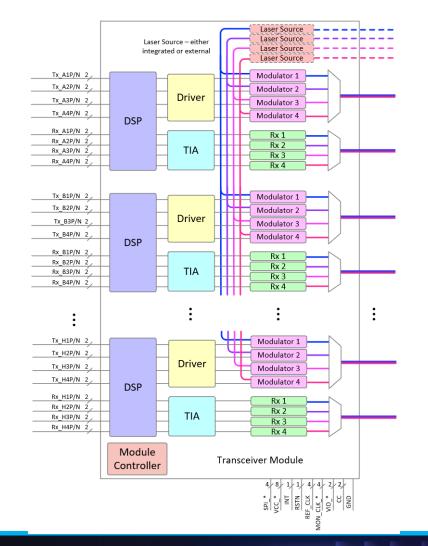

## **3.2T Optical Module Functionality** 3.2T Optical Module

• FR Module example ->

- How does this all fit in?

- 3D integration

- Die/functionality integration

- Optics (Laser + Modulator + PD)

- EIC (Driver/TIA/Control)

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF

# Energy Efficient Interfaces @ ECOC 2024

Energy Efficient Interfaces (EEI)

- EEI Interoperability agreements

- Co-Packaging Framework Document

- **3.2T** Optical Module for Co-Packaging Project

- 📫 🛛 🖬 ELSFP Project

- Electrical Interfaces for Co-Packaging

### Interoperability Demonstrations

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF

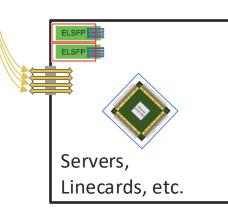

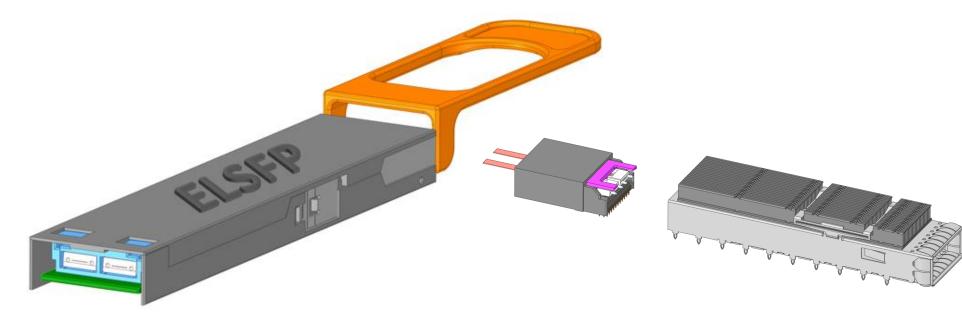

### Why ELSFP? ELSFP Project

• OIF defining common External Laser Pluggable

ELSEP

20

- Industry need for co-packaged and near-packaged systems

- Systems need faceplate density

- External laser modules need common specification for economies of scale

- Form factor to span multiple system generations

- Plan for optical & thermal scaling

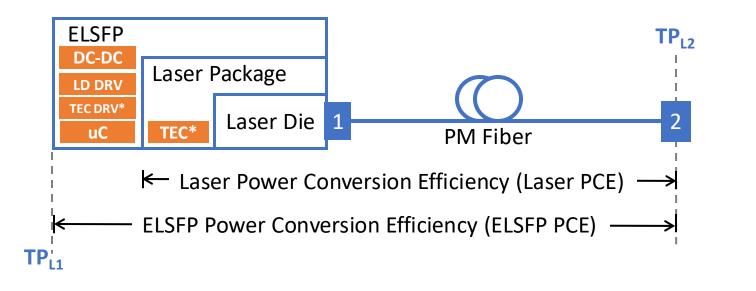

## External Laser Small Form Factor Pluggable (ELSFP)

- ELSFPs provide CW laser power for optical engines (OEs).

- Decreases thermal power density in the system

- Each large system will likely need multiple (i.e. 8 or 16) ELSFPs

- The light from a given ELSFP can feed more than a single OE.

- A pluggable form factor helps to ensure total system reliability and a "hot swap" replacement if a single laser or ELSFP module fails.

- Eye safety is achieved by a blind mate optical connector internal to the system.

21

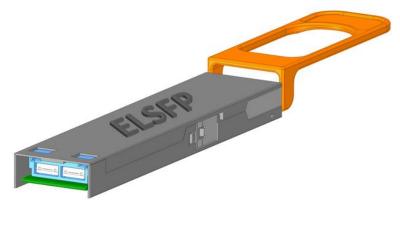

## Initial Technical Concept

**ELSFP** Project

## Density

- Blind mate pluggable

- Width similar to OSFP (16 modules wide with standard management I/O)

## Commonality

- Industry standard 3.3V Supply

- CMIS (Common Management Interface Specification)

22

## Scaling

- Optical Power Classes

- Thermal Power Classes

- Belly-to-belly configurations

- Riding heat sink for system flexibility

- 2 "MT like" ferrules for future proofing

- Support for 8 PM fibers per MT

- Support for multiple OE modules

### Single Port ELSFP Design ELSFP Project

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF

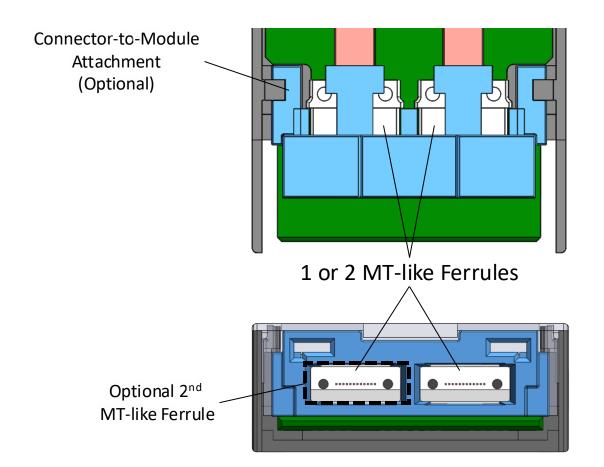

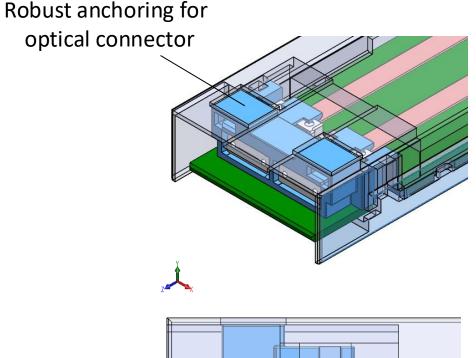

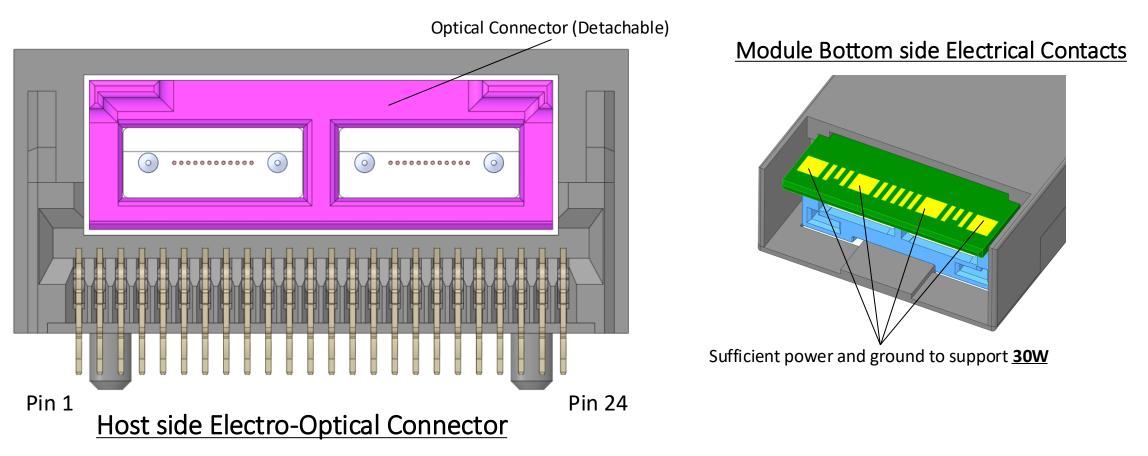

# **ELSFP Module-Side Optical Connector**

24

## **ELSFP Electro-Optical Connector**

Additional pins for control/management, laser safety (i.e. presence pin), and spares for future proofing Optical connector sub-assembly (pink) is separable from the board mounted electrical connector sub assembly

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF

## **ELSFP Optical Power Classes**

| ELSFP<br>Optical Power Classes | Power/λ/Core<br>+/- 1.5dB |                            |

|--------------------------------|---------------------------|----------------------------|

| Super Low Power - SLP          | 2dBm                      |                            |

| Ultra Low Power - ULP          | 5dBm                      | Combs                      |

| Very Low Power - VLP           | 8dBm                      |                            |

| Low Power - LP                 | 11dBm                     | Single-                    |

| Medium Power - MP              | 14dBm                     |                            |

| High Power - HP                | 17dBm                     |                            |

| Very High Power - VHP          | 20dBm                     | _ Multi-                   |

| Ultra High Power - UHP         | 23dBm                     | Channel                    |

| Super High Power - SHP         | 26dBm                     | *Naming con<br>Radio Frequ |

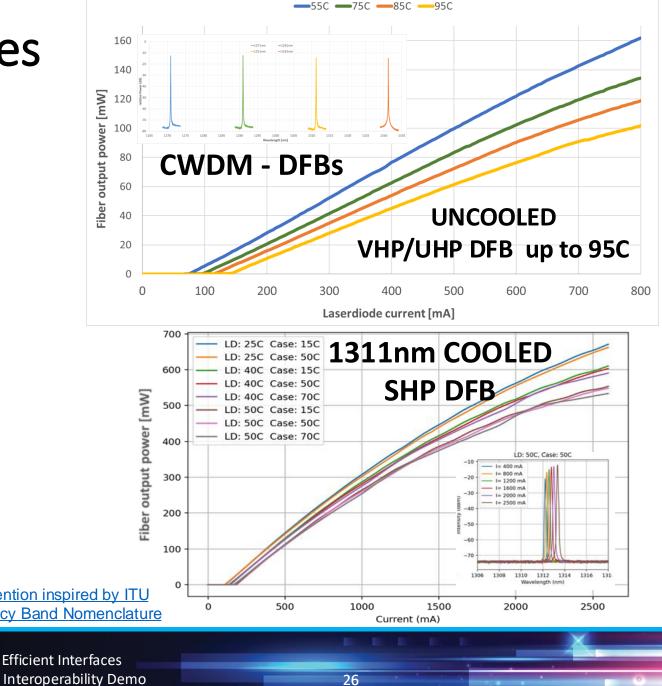

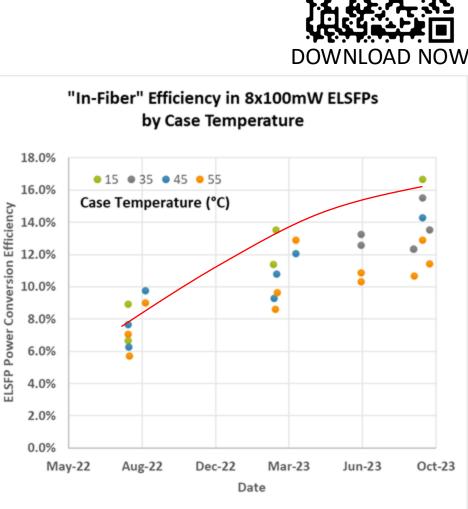

# ELSFP's eco-system drives innovation

The ELSFP's eco-system continues to innovate and has yielded impressive improvements in energy efficiency (PCE), a key component of next generation energy efficient interfaces

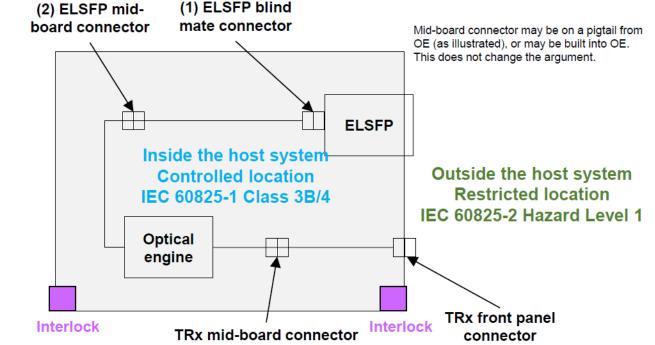

# Eye Safety

ELSFP's blind mate optical connector paired with a system interlock enables a safer co-packaged system implementation for users.

28

Similar to EDFAs with powerful CW lasers, Class 3B and 4 lasers can be used inside ELSFP and systems can be deployed in unrestricted locations.

# Energy Efficient Interfaces @ ECOC 2024

Energy Efficient Interfaces (EEI)

- EEI Interoperability agreements

- Co-Packaging Framework Document

- **3.2T** Optical Module for Co-Packaging Project

- ELSFP Project

- Electrical Interfaces for Co-Packaging

### Interoperability Demonstrations

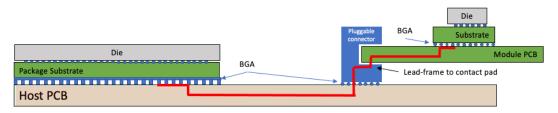

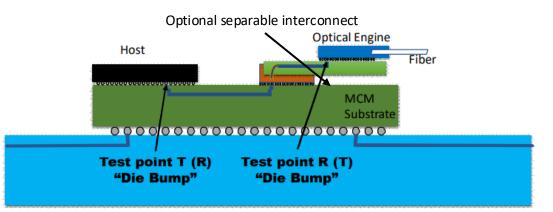

## CEI – An Essential Building Block for Co-packaging

#### Pluggable Module Channel Example Illustration

- Channel loss: 16dB ball to ball (22-24dB bump to bump)

- Typical pluggable connectors: IL of ~1dB with RL of -10dB @26.5GHz

#### **CPO/NPO Channel Example Illustration**

- Channel loss: CPO 10dB bump to bump; NPO 13dB bump to bump

- Optional separable interconnect performance example: LGA socket: IL of ~0.05dB with RL of -40dB @26.5GHz (<u>oif2020.341.01</u>, Nathan Tracy)

30

- Avoids/reduces major discontinuities.

- Optical modules are not end user pluggable.

- Significant power saving opportunity over VSR to be captured.

- A broad interoperable ecosystem is the key to success and can only be achieved through standardization.

## CEI-112G-XSR-PAM4 for Co-packaging

| Category | IL at Nyquist (Max, dB) | BER (Max) |

|----------|-------------------------|-----------|

| CAT1     | 10                      | 1e-6      |

| CAT2     | 10                      | 1e-8      |

| CAT3     | 8                       | 1e-9      |

- Baud rates supported: 36 Gsyms/s to 58 Gsyms/s

- Based on loss and jitter budgets between TX and RX using copper signal traces in a SIP(System in a Package) to enable low power consumption

- Three channel categories are defined, allowing optimization for various applications.

- Timeline

- Project started in April 2018.

31

• Draft specification is becoming technically stable. Few pending items to be addressed.

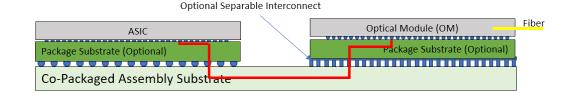

## CEI-112G-XSR+ -PAM4 for Near Packaging

- The emergence of Near Package Optics (NPO) Architecture

- Co-packaging requires significant package substrate size increase and technology advancement, which adds risk to goals of availability, cost and multi-vendor support.

- Instead of a monolithic package approach, Near Packaging relies on advanced PCB technology for dense high-speed routing without significant power penalty.

- Near Packaging architecture takes advantage of existing technologies and more robustly enables an open ecosystem implementation.

- Additional margin also strengthens a broader supply base for co-packaging implementation and adoption.

- Baud rates supported: 36 Gsyms/s to 58 Gsyms/s

- Optimize for Ethernet rate @ 106.25Gbps the key application for CPO/NPO

- Insertion loss < 13dB @ 26.5625GHz Nyquist bump to bump with up to 1 separable interconnect.

- Enable the lowest practical energy consumption (pJ/b) implementation.

- Leverage specification methodology and other work from existing CEI 112 projects.

**Optional Separable Interconnect**

# Energy Efficient Interfaces @ ECOC 2024

Energy Efficient Interfaces (EEI)

### EEI Interoperability agreements

- Co-Packaging Framework Document

- 3.2T Optical Module for Co-Packaging Project

- ELSFP Project

- Electrical Interfaces for Co-Packaging

- Compute Optics Interface (COI)

- Retimed Transmitter Linear Receiver (RTLR)

### Interoperability Demonstrations

# EEI ELSFP - External Laser Small Form Factor

**G**/Accelink

SENKO<sup>®</sup> Advanced Components

### **Demonstrating 4 ELSFP modules showcasing the ecosystem**

- Lasers: 8 lasers per module (1310nm)

- Output power: 23 dBm (UHP)

- Both cooled and uncooled lasers

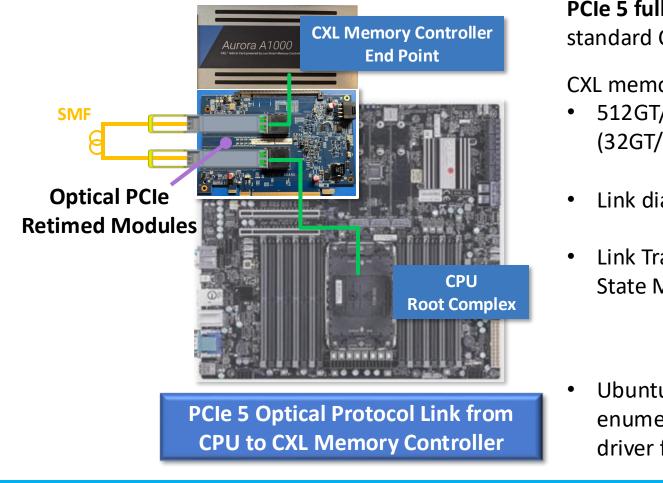

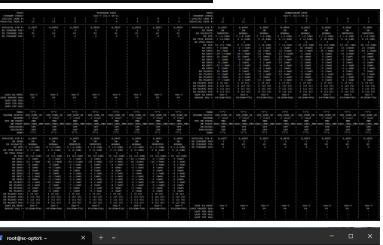

## PCIe Protocol over Optics I (OS Enumeration)

PCIe 5 full protocol link over optics using industry standard CPU and (first public demonstration)

### CXL memory controller

- 512GT/s link capacity (32GT/s x 8 x 2)

- Link diagnostics

- Link Training and Status State Machine (LTSSM)

Ubuntu server OS shows enumerated PCIe device driver from the BIOS/OS

| į                          |                                              | PATH STATE               | ES                                                       |                                  |

|----------------------------|----------------------------------------------|--------------------------|----------------------------------------------------------|----------------------------------|

| <br>  ртн                  | Upstream Path<br>STATE                       | <br>SPEED   PTH          | Downstream Pa<br>I STATE                                 | th<br>SPEED                      |

| 04<br>  06<br>  08<br>  10 | 0x13>FWD<br>0x13>FWD<br>0x13>FWD<br>0x13>FWD | Gen-5   07<br>Gen-5   09 | 0x13>FWD<br>0x13>FWD<br>0x13>FWD<br>0x13>FWD<br>0x13>FWD | Gen-5<br>Gen-5<br>Gen-5<br>Gen-5 |

XLCt1: Cache-

35

USCONEC

AsteraLabs.

**/iNNO'LIGHT**

De-emphasis Level: -6dB

Memory Device (

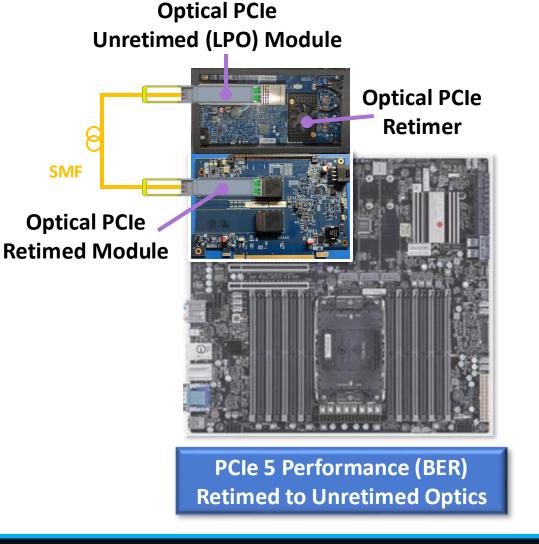

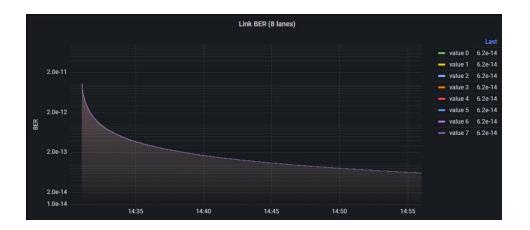

# PCIe Protocol over Optics II (Performance)

### Retimed module to unretimed module

- Integrated Retimed Module (Astera Labs), to

- Unretimed LPO Module (Accelink or Innolight)

- Demonstrating performance <<1e-12

Running live prbs data stream x 8 bi-directional, error free

BER live graph (BER reducing further vs time captured)

36

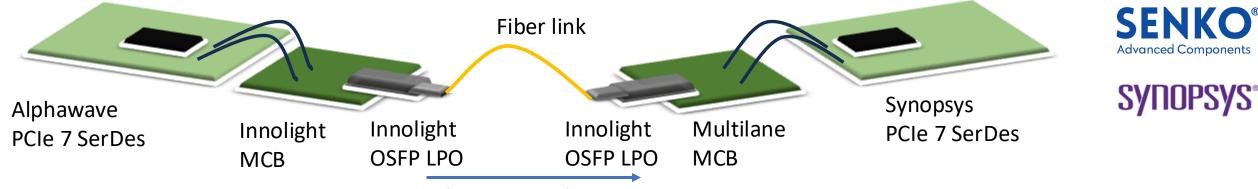

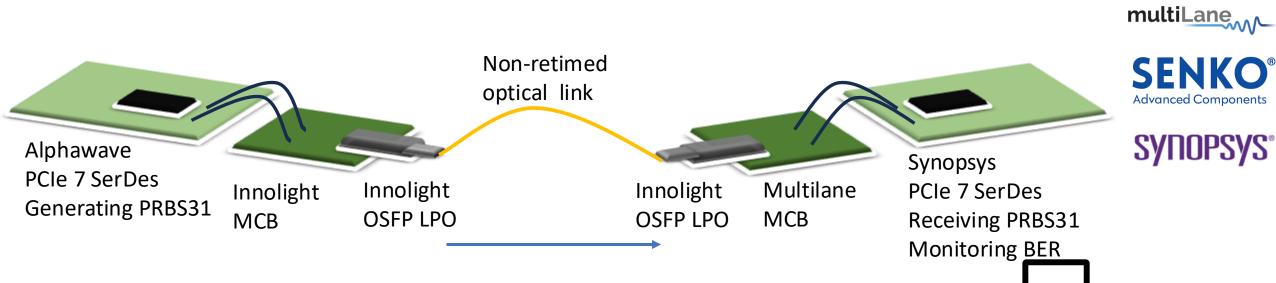

# PCle 7.0 Performance Over Optics

DR4 showing one lane active

This PCIe 7.0 over Optics demonstration features a test chip silicon TX transmitting PRBS 31 PAM4 at 128Gbps over an optical link. The setup includes an Innolight module compliance board mated with an Innolight linear pluggable optical module (LPO) over a fiber optics channel. This is connected to another Innolight linear pluggable optical module (LPO ),which is mated with a Multilane module compliance board. The test chip silicon RX then receives the PRBS 31 signal at 128Gbps. The receiver test chip demonstrates bit error rate (BER) performance and displays the received eye diagram over a linear optical link

#### Key points:

Demonstrates a developing eco-system enabling energy efficient link capable of transporting PCIe data rates

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF

# PCle 7.0 Performance Over Optics

Demonstrating an optical link carrying 128Gbps traffic at PCIe7 data rates

Data Signal: PCIe7 (128Gbps PRBS31 PAM4)

**Optical Link**: 800GBASE-DR4 OSFP linear modules supporting 128Gbps traffic

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF

# RTLR (Retimed Tx, Linear Rx)

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF

39

Accelink

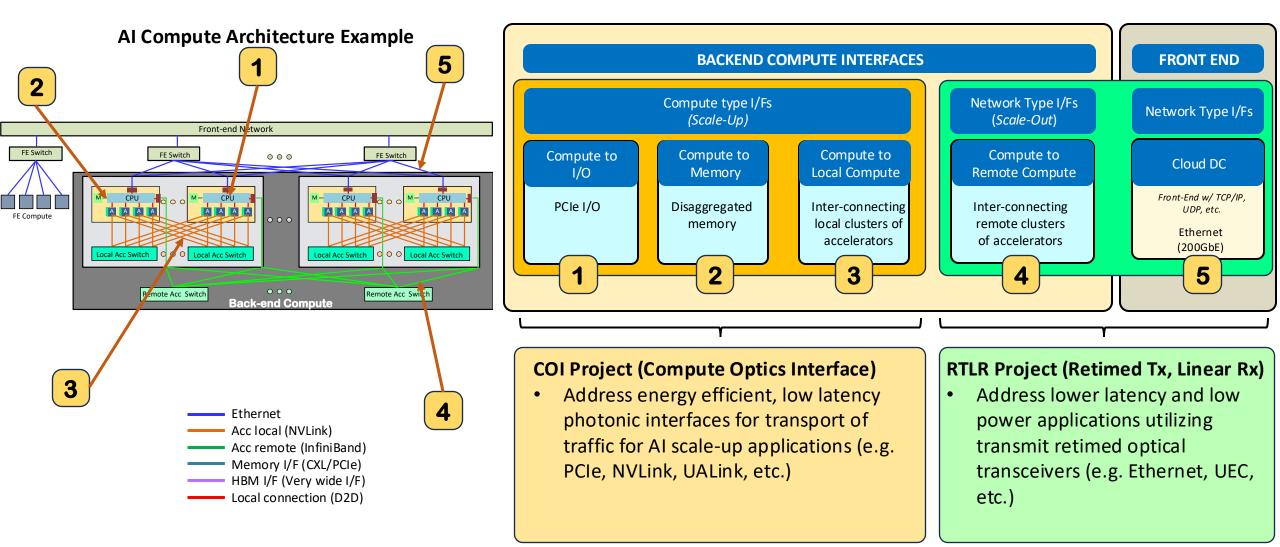

# **Conceptual Demo for AI Compute**

### **Depicting an AI Backend Compute and its various links**

**Compute Chassis**

Showing an array of compute and switch cards interconnected with a variety of optical connectivity options

Next Gen switch card located in Compute Chassis Highlighting an ASIC with 4T/mm edge bandwidth and Ethernet interfaces on board. Optical links powered by ELSFP

AsteraLabs.

#### Accelerator Cards

Variety of next gen PCIe compute cards plugged into a PCIe chassis

AI backend compute employs low latency links to interconnect local accelerators in a cache coherent way. The local links are typically PCIe-like (NVLink, UALink, etc).

Groups of compute clusters are interconnected with lower latency Ethernet / InfiniBand connections

Energy Efficient Interfaces OIF's ECOC Interoperability Demo Copyright @ 2024 OIF

# Accelink